- 1. Simplify the following boolean expressions:

- (a)  $Q_A(Q_B\overline{Q_C} + Q_BQ_C) + \overline{Q_B}$ (b)  $\overline{\overline{A \,\overline{B} + C} + \overline{A}C + \overline{B}}$ (c)  $xyz + \overline{x}\,\overline{y}z + \overline{x}yz + \overline{x}y\overline{z} + \overline{x}\,\overline{y}\,\overline{z}$

- 2. Consider the below truth tables expressed in Karnaugh-map style:

| K-map III: |                                                                              |  |  |

|------------|------------------------------------------------------------------------------|--|--|

| CD         |                                                                              |  |  |

| 01 11      | 10                                                                           |  |  |

| 1 0        | 1                                                                            |  |  |

| 0 x        | 0                                                                            |  |  |

| 1  0       | х                                                                            |  |  |

| x 1        | 1                                                                            |  |  |

|            | $\begin{array}{c} CD\\ 01 & 11\\ \hline 1 & 0\\ 0 & x\\ 1 & 0\\ \end{array}$ |  |  |

Directly on each of the above K-maps make *one* 'circle' capturing largest number of 1s properly (i.e., incluing no 0s). Report the particular boolean expression that is selected by the circled region. (For some maps there may be several equally good choices for the "largest proper selection".)

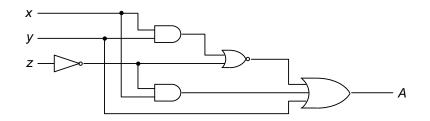

3. Consider the below mess of gates:

- (a) Convert the mess of gates into the equivalent boolean expression.

- (b) Simplify this your boolean expression.

- (c) On this sheet of paper, label each gate with its usual name (I'm seeking a name like XOR not a number like 7486) and label the logic level of each wire for inputs: (x, y, z) = (0, 0, 0).

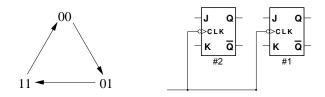

4. A 3-state diagram for two binary digits  $Q_2Q_1$  is displayed below.

Using two edge-triggered JKFFs design a synchronous circuit that follows the above state diagram, where the two binary digits  $Q_2Q_1$  are the outputs of the JKFFs. You will need to determine how the outputs of the two JKFFs:  $Q_i$  generate the required inputs of the two JKFFs  $(J_iK_i)$ .

(a) Begin by considering the possible transitions of a single JKFF. What values of JK allow a particular transition? Fill in the below table. Hint: in every row either J or K will be an X for "don't care".

| Transition:           | J | K |

|-----------------------|---|---|

| $0 \longrightarrow 0$ |   |   |

| $0 \longrightarrow 1$ |   |   |

| $1 \longrightarrow 0$ |   |   |

| $1 \longrightarrow 1$ |   |   |

(b) Fill in the below table so desired cycle is followed.

| ( | $Q_2$ | $Q_1$ | $J_2$ | $K_2$ | $J_1$ | $K_1$ |

|---|-------|-------|-------|-------|-------|-------|

|   | 0     | 0     |       |       |       |       |

|   | 0     | 1     |       |       |       |       |

|   | 1     | 1     |       |       |       |       |

- (c) Controls for  $J_1$ ,  $K_1$ ,  $J_2$ , and  $K_2$  can be easily generated—what are they?

- (d) What happens to the state 10?

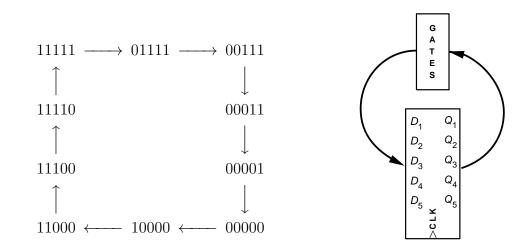

5. The Morse Code for the digits 0–9 consist of five bits  $Q_1Q_2Q_3Q_4Q_5$  with 0=11111, 1=01111, 2=00111, 3=00011, etc. (0=dot, 1=dash). Consider a Morse Code decade counter that cycles around consecutively displaying the Morse Code pattern for the digits 0–9 (and back to 0), as shown below:

(a) Fill in the below table so it displays the desired cycle and the  $D_i$  required to generate it.

| $Q_1$ | $Q_2$ | $Q_3$ | $Q_4$ | $Q_5$ | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 1     | 1     | 1     | 1     | 1     |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

|       |       |       |       |       |       |       |       |       |       |

- (b) Write down the minterm (Sum-of-Products) expression for  $D_1$ . Use boolean algebra to simplify (gate reduce) the expression. Show the circuit for your simplified boolean expression.

- (c) Notice that in fact  $D_1 = \overline{Q_5}$  would work. Find equally simple expressions for  $D_2, D_3, D_4$ , and  $D_5$ . With these simple expressions find the future of the state: 10101... does it connect into the above cycle?

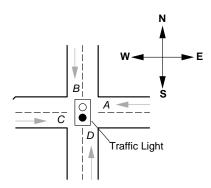

6. A simple green/red traffic light (just go/stop—no amber—allowing two way traffic N-S xor E-W) is placed at an intersection of a N-S running road and a E-W running road. Four sensors (*ABCD*) are placed in the traffic lanes allowing an array of gates to control the traffic light. The sensors are identical: each will go HIGH (1) if a vehicle is above it and will be LOW (0) otherwise.

The traffic light is to follow the following rules:

- If E-W is green, N-S is red, and vice versa.

- E-W is green whenever lanes A and C are both occupied.

- E-W is green whenever either lanes A or C are occupied and lanes B and D are not both occupied.

- N-S is green whenever lanes B and D are both occupied and lanes A and C are not both occupied.

- N-S is green whenever either lanes B or D are occupied and lanes A and C are both vacant.

- E-W will be green when no vehicles are present.

Write out the truth table giving the N-S light control (1 for green, 0 for red) in terms of the inputs ABCD.