## Part I

- 0. You investigate here two counters: the '163 (a fully synchronous, presettable binary counter) and the '191 (an up/down binary counter with asynchronous load). (Note: some protoboard 'debounced pushbuttons' will produce multiple pulses each push. If your counting seems anomalous, try clocking with the TTL function generator.)

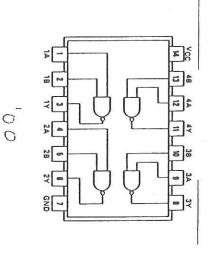

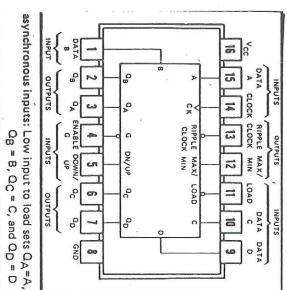

- 1. Press in, and power "at the counters", the following TTL chips (from top to bottom): 74191 (up/down counter), 7400 (quad NAND), and two 74163s (counter).

- 2. Using the top '163, tie ENABLE T high, take ENABLE P, CLEAR, LOAD, and the data inputs D, C, B, and A to data switches and the outputs: CARRY OUTPUT,  $Q_D$ ,  $Q_C$ ,  $Q_B$ , and  $Q_A$  to LEDs. Begin by clocking with a NC pushbutton (remember the pull-up resistor). Note that to count, ENABLE P, CLEAR, and LOAD must all be high. Does the '163 count positive-going edges or negative-going edges? (Report your evidence!) Describe when CLEAR and LOAD need to be set and when the corresponding action occurs. Describe exactly how you would use LOAD to set the counter to 7. Carefully sketch (stacked format) the CARRY OUTPUT, CLOCK and counter value (converted to decimal) as you move towards and beyond the top count. Move the clock input from the pushbutton to the protoboard's function generator (on TTL). Set the clock rate to ~1 Hz and observe the up-counting action.

- 3. Make a decade counter by detecting the ones in a 9-count output using a NAND and feeding the NAND output to CLEAR. Does your decade counter briefly hit 10 before clearing? Use another NAND to detect a 10 count and look for glitches with a logic probe. (Diagram how you did this!) Make 7,8,9 cycle by enabling a load of 7 following the detection of 9. Draw these circuits!

- 4. How can the carry be used to achieve synchronous 8-bit counting shared between two '163s? Note that using the carry as a clock to the second chip fails as the second clock tics one count too soon. (On your above stacked traces, label where such clocking would occur.) Inverting the carry would work, but would lead to a ripple counter. If two ICs are to be synchronous they must use exactly the same clock. (Hint: If the chips are clocked by the same signal, but one chip's count changes and the other's count does not, the inactive chip must be disabled.) Make a synchronous binary counter with 8 bits of output. Now make your two-163 counters have a top count of 20. Show the result to your instructor. Draw the circuit! (Your solution should be easily modifiable to make any number, e.g., 160, the top count.)

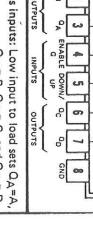

- 5. Investigate the behavior of the '191 as in #2. Note that LOAD must be high and ENABLE G low to count. Note that there is no CLEAR. Don't worry about the two types of carry: MAX/MIN and RIPPLE CLOCK. Describe how the up/down pin affects the counting. What sort of edge triggers the '191? What evidence shows that the '191 is asynchronous whereas the '163 is synchronous?

## Part II

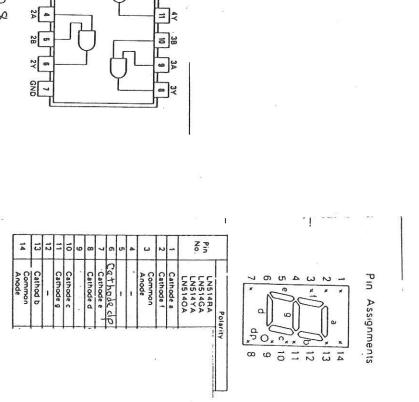

- 0. In this part you will investigate a higher level of function integration available in the 74143. This chip is a 4-bit counter, a 4-bit latch, and a seven-segment decoder/driver all in one package. This chip is designed to drive common-<u>anode</u> displays (N.B., *not* the common-<u>cathode</u> displays we used in the last lab). In a common-anode display, the high side of all the segments are internally connected together and that common-anode pin needs to be connected to +5 V. An individual segment is lit by connecting the low side of that segment "to ground." *Recall that you never actually connect a segment between ground and power as it will burn out in a quick fizzle.* The current must be somehow limited (in this case to about 15 mA). This current-limiting feature is built into the '143.

- 1. After removing the chips from Part I, press in (top to bottom) and power up (at the corners for the chips) a '08 (quad AND), a '143, a seven-segment display, another '143 and another display. Read the spec sheet and decide how to wire-up the various inputs so that the '143 will continuously display and count the clock input. Make a table reporting the logic level required on each input for this normal counting. Does the '143 count positive or negative edges? Note particularly the PARALLEL COUNT ENABLE INPUT, CLEAR, and the LATCH STROBE INPUT. Describe how/when each of these works. As you did for the '163, carefully sketch (stacked format) the MAX COUNT, CLOCK and counter value (converted to decimal) as you move towards and beyond the top count.

- 2. Figure out how you can chain your two '143s to get a two-decimal-digit count. Provide a brief circuit diagram of your solution. Is your circuit synchronous or asynchronous?

- 3. Make a simple stop watch using the AND as a clock gate. Wire-up CLEAR and LATCH STROBE INPUT as in a normal stop watch (i.e., include a lap-time, a reset, and start/stop options). (If you want to be fancy and include a pushbutton toggle-action start/stop, you'll need a JKFF.) Demonstrate the circuit to your instructor; write down how your circuit accomplishes these tasks (or draw the circuit).

| TEXAS INSTRUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                     | TEX                                                                         | 2                                                                                                            | 284 | TEXAS INSTRUMENTS                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                             |                                                                                                              | 1   | Tredomark of RCA                                                                                                                                                                                                                                                                                                                                                                       |

| pull-up circuit suitable for performing a wire-AND function with any<br>open-collector output. Whenever this pin is low the entire display will be<br>blanked; therefore, this pin may be used as an active-low blanking input.<br>Outputs for driving seven-segment LED's or lamps and their decimal<br>points. See segment identification and resultant displays on following<br>page.                                                              | 15, 16, 14, 9<br>11, 10, 13, 8                                              | LED/LAMP DRIVER<br>OUTPUTS<br>(a, b, c, d, e, f, g, dp)                                                      |     | The SN54143 and SN74143 driver outputs are designed specifically to maintain a relatively constant on-level sink<br>current of approximately 15 milliamperes from outputs "a" through "g" and seven milliamperes from output "dp"<br>over a voltage range from one to five volts. Any number of LED's in series may be driven as long as the output voltage<br>rating is not exceeded. |

| Supplies ripple blanking information for the ripple blanking input of the next decade. Provides a low if BI is high, or if ABI is low and the data in the latches in BCD 0; otherwise, this output is high. This pin has a resistive                                                                                                                                                                                                                  | თ                                                                           | RIPPLE-BLANKING<br>OUTPUT (RBO)                                                                              |     | input transistors to lower drive-current requirements to one-half of that required for a standard Series 54/74 TTL input.<br>The serial-count-enable, actually two internal emitters, is rated as one standard series 54/74 load. The logic outputs,<br>except RBO, have active pull-ups.                                                                                              |

| When the data in the latches is BCD 0, a low input will blank the entire display and force the RBO low. This input has no effect if the data in the latches is other than 0.                                                                                                                                                                                                                                                                          | 4                                                                           | RIPPLE-BLANKING<br>INPUT (RBI)                                                                               |     | description<br>These TTL MSI circuits contain the equivalent of 86 gates on a single chip. Logic inputs and outputs are completely<br>TTL/DTL compatible. The buffered inputs are implemented with relatively large resistors in series with the bases of the                                                                                                                          |

| When high, will blank (turn off) the entire display and force RBO low.<br>Must be low for normal display. May be pulsed to implement intensity<br>control of the display.                                                                                                                                                                                                                                                                             | თ                                                                           | (BI)                                                                                                         |     | Look-Ahead-Enable Techniques Minimize Speed Degradation When Cascaded for Large-Word Display<br>Direct Clear Input                                                                                                                                                                                                                                                                     |

| Must be high to display decimal point. The decimal point is not displayed when this input is low or when the display is blanked.                                                                                                                                                                                                                                                                                                                      | 7                                                                           | DECIMAL POINT                                                                                                |     | <ul> <li>Synchronous BCD Counter Capability Includes:</li> <li>Cascadable to N-Bite</li> </ul>                                                                                                                                                                                                                                                                                         |

| The BCD data that drives the decoder can be stored in the 4-bit latch and is available at these outputs for driving other logic and/or processors. The binary weights of the outputs are: $O_A = 1$ , $O_B = 2$ , $O_C = 4$ , $O_D = 8$ .                                                                                                                                                                                                             | 17, 18, 19, 20                                                              | LATCH OUTPUTS<br>(QA, QB, QC, QD)                                                                            |     | Ripple Blanking of Extraneous Zeros<br>Latch Outputs Can Drive Logic Processors Simultaneously<br>Decimal Point Driver Is Included                                                                                                                                                                                                                                                     |

| When low, data in latches follow the data in the counter. When high, the data in the latches are held constant, and the counter may be operated independently.                                                                                                                                                                                                                                                                                        | 21                                                                          | LATCH STROBE<br>INPUT                                                                                        |     | SN54144 and SN74144 Drive High-Current Lamps, Numitrons <sup>†</sup> , or LED's from Saturated Open-Collector Outputs<br>• Universal Logic Capabilities                                                                                                                                                                                                                                |

| Will go low when the counter is at 9 and serial count enable input is low.<br>Will return high when the counter changes to 0 and will remain high during<br>counts 1 through 8. Will remain high (inhibited) as long as serial count<br>enable input is high.                                                                                                                                                                                         | 22                                                                          |                                                                                                              |     | <ul> <li>Choice of Driver Outputs:</li> <li>SN54143 and SN74143 have 15-mA Constant-Current Outputs for Driving Common-Anode LED's such as TIL302 or<br/>TIL303 without Series Resistors</li> </ul>                                                                                                                                                                                    |

| Must be low for normal counting mode, also must be low to enable<br>maximum count output to go low. When high, counter will be inhibited<br>and maximum count output will be driven high. Logic level must not be<br>changed when the clock is low.                                                                                                                                                                                                   |                                                                             | SEMIAL COUNI<br>ENABLE INPUT (SCEI)                                                                          | eu  | logic: see description                                                                                                                                                                                                                                                                                                                                                                 |

| Must be low for normal counting mode. When high, counter will be inhibited. Logic level must not be changed when the clock is low.                                                                                                                                                                                                                                                                                                                    | 23                                                                          | ENABLE INPUT (PCEI)                                                                                          |     |                                                                                                                                                                                                                                                                                                                                                                                        |

| Each positive-going transition will increment the counter provided that the<br>circuit is in the normal counting mode (serial and parallel count enable<br>inputs low, clear input high).                                                                                                                                                                                                                                                             | N                                                                           |                                                                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                        |

| DESCRIPTION<br>When low, resets and holds counter at 0. Must be high for normal<br>counting.                                                                                                                                                                                                                                                                                                                                                          | PIN NO.                                                                     | FUNCTION<br>CLEAR INPUT                                                                                      |     |                                                                                                                                                                                                                                                                                                                                                                                        |

| Functions of the inputs and outputs of these devices are as follows:                                                                                                                                                                                                                                                                                                                                                                                  | and outputs of                                                              | Functions of the inputs                                                                                      |     |                                                                                                                                                                                                                                                                                                                                                                                        |

| All inputs are diode-clamped to minimize transmission-line effects, thereby simplifying system design. Maximum clock frequency is typically 18 megahertz and power dissipation is typically 280 milliwatts. The SN54143 and SN54144 are characterized for operation over the full military temperature range of $-55^{\circ}$ C to $125^{\circ}$ C; the SN74143 and SN74144 are are characterized for operation from $0^{\circ}$ C to $70^{\circ}$ C. | mped to minimiz<br>8 megahertz and<br>ion over the full<br>tration from 0°C | All inputs are diode-cla<br>frequency is typically 1<br>characterized for operat<br>are characterized for op |     |                                                                                                                                                                                                                                                                                                                                                                                        |

| The SN54144 and SN74144 drivers have high-sink-current saturated outputs for driving indicators having voltage<br>ratings up to 15 volts or requiring up to 25 milliamperes drive. The SN54144 sinks 20 milliamperes and the SN74144<br>sinks 25 milliamperes at an on-level voltage of 0.6 volts across their respective operating temperature ranges.                                                                                               | 74144 drivers h<br>r requiring up to<br>an on-level volta                   | The SN54144 and SN<br>ratings up to 15 volts o<br>sinks 25 milliamperes at                                   |     | MAX STROBE                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                             | description (continued)                                                                                      |     | J OR N DUAL-IN-LINE OR                                                                                                                                                                                                                                                                                                                                                                 |

| TYPES SN54143, SN54144, SN74143, SN74144<br>4-BIT COUNTER/LATCH, SEVEN-SEGMENT LED/LAMP DRIVERS                                                                                                                                                                                                                                                                                                                                                       | N54144, SI<br>TCH, SEVE                                                     | TYPES SN54143, S<br>4-BIT COUNTER/LA                                                                         |     | MSI 4-BIT COUNTER/LATCH, SEVEN-SEGMENT LED/LAMP DRIVERS                                                                                                                                                                                                                                                                                                                                |

æ

I EAAS INSTRUMENTS INCORPORATED

VCC OUTPUT OA

08

8

ENABLE LOAD

OUTPUTS

16

5

14

ದ \_\_\_\_\_\_

12

= 00

5

6

CAHHY OA

OB

ര

OD ENABLE

CLEAR

LOAD

S S

8

O ENABLE

CLEAR

CLOCK

163 DATA INPUTS 2

60

.sm

ഗ

ത

-

00

σ

ENABLE GND

191

0 %

5-

10

₹[•