Note: A.C. voltages and currents are recorded here as rms quantities unless otherwise stated. (Your answers should also be rms quantities unless the problem requests otherwise.) Numerical answers should be reported with three significant digits.

- 1. Suppose three resistors (1 k $\Omega$ , 2 k $\Omega$ , and 3 k $\Omega$ ) are connected in series and powered with a 12 V battery.

- (a) Draw a schematic diagram of the situation.

- (b) What current (in mA) flows from the battery? What power (in mW) is produced by the battery?

- (c) What is the voltage across each resistor? What is the current through each resistor?

- 2. Suppose three resistors (1 k $\Omega$ , 2 k $\Omega$ , and 3 k $\Omega$ ) are connected in parallel and powered with a 12 V battery.

- (a) Draw a schematic diagram of the situation.

- (b) What current (in mA) flows from the battery? What power (in mW) is produced by the battery?

- (c) What is the voltage across each resistor? What is the current through each resistor?

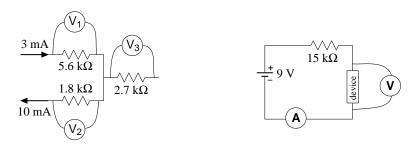

- 3. Kirchhoff's Laws: See the below figures.

- (a) A current of 3 mA flows into one wire of a circuit consisting of 3 resistors, and 10 mA flows out another wire. Report the readings on the three voltmeters. Draw a schematic diagram showing which lead on each voltmeter is the 'red' lead.

- (b) An unknown device is connected in a circuit with a 9 V battery and a 15 k $\Omega$  resistor. The ammeter reads 0.5 mA. What does the voltmeter read?

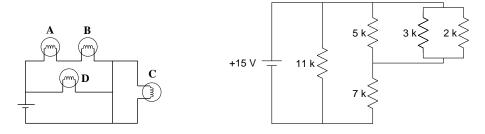

4. Which light bulb in the below left circuit shines the brightest? Why? Which light bulb shines the dimmest? Why?

- 5. Consider the circuit diagrammed above right. Find the current flowing in each resistor. (Note: in this schematic (and many others) resistor values are listed without the  $\Omega$  unit; "k" in this context means "k $\Omega$ ".)

- 6. What is the (warm) resistance of a 100 W light bulb operating from a 120 V source?

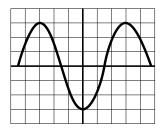

7. The below left diagram shows a single sinusoidal scope trace. Determine: the peak-to-peak voltage, the voltage amplitude, the rms voltage, the wave period and frequency. Assume that the bottom of the scope display reads:

CH1 500mV

M 5.00ms

Ext / 0.00V

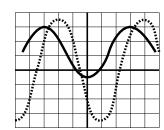

- 8. The above right diagram shows a pair sinusoidal scope traces. Assume that the scope controls are set as in the previous problem with CH 2 (dotted) and CH 1 (solid) identical. Which trace is lagging: dotted or solid? What is the phase shift in degrees?

- 9. Manufacturers typically report DMM errors as a percentage of the reading plus a certain number of "digits". In this context, one digit means a 1 in the rightmost displayed digit and zeros everywhere else. Consider a DMM display: 0.707. Find the error in this reading if the device is:

- (a) MeTex-3800 DC current, 2 mA range.

- (b) MeTex-3800 AC current at 500 Hz, 2 A range.

- (c) Keithley 169 resistance, 2 k $\Omega$  range.

- (d) Keithley 169 AC volts at 2 kHz, 2 V range.

The specification sheets can be found posted in the lab or in the manuals in the physics library. As always, errors should be rounded to one or two significant figures.

- 10. Work the previous problem assuming the display reads: 0.007

- 11. An a.c. voltage source follows the equation:  $v(t) = A \sin(\omega t + \phi) + B$  where A = 5 V, B = 1 V,  $\omega = 1000$  rad/s, and  $\phi = .45$  rad. Report values for the following:

(a) average voltage (d.c. offset)

(e) rms voltage

(b) voltage amplitude

(f) voltage at t=0

(c) peak voltage

(g) frequency

(d) peak-to-peak voltage

(h) period

- 12. A function generator has an output impedance of 50  $\Omega$  and, when unloaded, produces a voltage amplitude of 10 V. What is the maximum (average) power that can be transferred to an external device attached to the function generator?

- 13. A circuit consists of an inductor (inductance L) connected directly to a 120 V, 60 Hz wall receptacle. What is the smallest L you could use and avoid blowing the 20 A fuse? A similar circuit consists of a capacitor connected directly to a wall receptacle. What is the largest C you could use and avoid blowing the fuse? In either case, the power company will bill you for 120 V×20 A = 2400 "Watts" of power. What is happening to all that "power"?

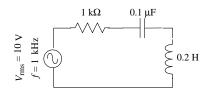

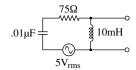

- 14. In the below circuit, find the voltage drop across each component and phase shift between that voltage and the current.

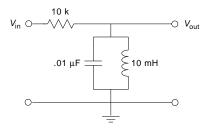

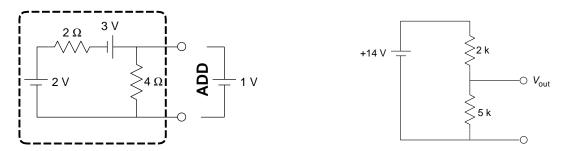

15. Consider the below circuit. Plot  $V_{\text{out}}$  as a function of frequency, where  $V_{\text{in}} = 10 \text{ V}$ . Plot the phase difference between  $V_{\rm out}$  and  $V_{\rm in}$  as a function of frequency. Your plotted frequency range should include frequencies such that  $X_C \gg X_L$  and  $X_C \ll X_L$ . (Hint: if  $z = Ae^{i\phi}$  for  $A, \phi \in \mathbb{R}$ , then in Mathematica A=Abs[z], and  $\phi=Arg[z]$ )

- 16. Work the previous problem again, but this time assume that the inductor is really a series combination of an ideal 10 mH inductor and a 100  $\Omega$  resistor. (Since inductors consist of a long thin wire wrapped into a coil, they typically have resistance in addition to inductance.)

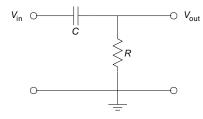

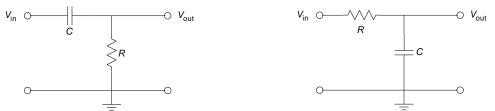

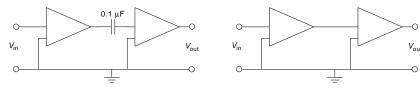

- 17. Consider the below left high pass filter with:  $V_{\rm in}=10~{\rm V}$  (at a frequency of 1 kHz),  $C=.01~\mu{\rm F}$ ,  $R = 10 \text{ k}\Omega$ . What is  $f_{-3\text{dB}}$  for this filter? Find:

- (a) current flowing

- (b) voltage across  $R(V_{\text{out}})$

- (c) voltage across C

- (d) the phase angle between  $V_{\text{out}}$  and  $V_{\text{in}}$

Draw a scope trace diagram similar to problem 8, showing  $V_{\rm in}$  (as a solid line) and  $V_{\rm out}$  (as a dotted line). Report the scale settings (VOLTS/DIV and TIME/DIV) used in your sketch.

- 18. Consider the above right low pass filter with:  $V_{\rm in}=0.1~{\rm V}$  (at a frequency of 1 kHz),  $C=6.8~\mu{\rm F}$ ,  $R = 50 \Omega$ . What is  $f_{-3dB}$  for this filter? Find:

- (a) current flowing

- (b) voltage across R

- (c) voltage across  $C(V_{\text{out}})$

- (d) the phase angle between  $V_{\rm out}$  and  $V_{\rm in}$

Draw a scope trace diagram similar to problem 8, showing  $V_{\rm in}$  (as a solid line) and  $V_{\rm out}$  (as a dotted line). Report the scale settings (VOLTS/DIV and TIME/DIV) used in your sketch.

- 19. The dual scope trace in problem 8 was produced by a series RC circuit driven with a function generator  $(V_{\rm in},$  at some frequency f; the dotted curve in the scope trace of problem 8). The output is taken across R or C ( $V_{\text{out}}$ , also at f; the solid curve in the scope trace). Both scope channels are on identical scales; you do not need the actual numerical values of the scope scales to answer the following questions.

- (a) Which signal is leading? What is the phase angle between  $V_{\rm in}$  and  $V_{\rm out}$ ?

- (b) Is the output taken across the resistor or the capacitor? Provide a schematic diagram of the circuit. Is this a high-pass or low-pass filter?

- (c) Is f above or below  $f_{-3dB}$ ? Calculate the ratio:  $f/f_{-3dB}$

20. Express the following complex numbers in  $r \angle \theta$  format (I bet your calculator can do this automatically):

(a)

$$\frac{1}{1+i}$$

(b)

$$\frac{3+i}{1+3i}$$

(c)

$$25e^2$$

(b)

$$\frac{3+i}{1+3i}$$

(c)  $25e^{2i}$  (d)  $(1/(1+i))^*$

(e)

$$\frac{1}{(1+i)}$$

21. Find the following in (a, b) format (I bet your calculator can do this automatically):

(a)

$$\frac{3i-7}{i+4}$$

(b)

$$(.64 + .77i)^4$$

(c)  $\sqrt{3 + 4i}$

(c)

$$\sqrt{3+4i}$$

(d)

$$25e^{2i}$$

(e)

$$\ln(-1)$$

22. LRC Circuit

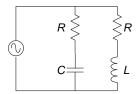

The circuit shown right includes two identical resistors (resistance R), an inductor (L), and a capacitor (C). Find the equivalent impedance, and show that if  $R = \sqrt{L/C}$ , the equivalent impedance does not depend on  $\omega!$

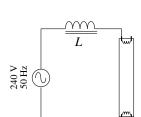

23. Fluorescent Lamp: run

In England (where the "mains" supply is 240 V at 50 Hz) fluorescent tubes are powered with the circuit shown. The inductor L("ballast") is used as part of a voltage divider to supply the tube with less than 240 V. Consider the case of the T12 24" 20 Watt tubes used in our halls. When lit, these tubes draw 0.37 A. Assuming the tube acts just like a resistor, what is the voltage across the tube? What value of L would provide this current and voltage in England?

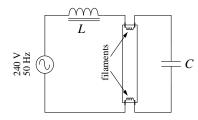

24. Fluorescent Lamp: LRC start?

In order to ignite the arc inside the fluorescent tube the filaments are heated (by sending a current through them) and then a high voltage pulse is applied. While not the usual method used, an LRC resonant circuit could be used to produce both a large filament current and a voltage well above 240 V, and thus facilitate the ignition. (The unlit tube acts is an insulator; the filaments are the R; use the value found in the previous problem for L.) If run exactly at resonance, what value of C is required? If the total filament resistance is 40  $\Omega$  how much current will flow? Find the voltage across the tube. Exact resonance would actually produce too much current. What value of C is required if the current is to be limited to 0.5 A?

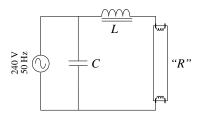

25. Fluorescent Lamp: power factor

As in the previous problems, a 20 Watt fluorescent tube, when lit, will draw 0.37 A from the assumed 240 V supply. The power company will then bill you for  $0.37 \text{ A} \times 240 \text{ V} = 90 \text{ "Watts"}$ whereas you are only using 20 W. Oddly enough you can reduce the current drawn from the receptacle by adding a capacitor in parallel to the tube+ballast. This "power factor correcting" capacitor results in a total impedance ( $\mathbf{Z}_{\text{total}}$ ) that is real (i.e., the current drawn from the receptacle is in phase with the voltage). Show that the required C is given by:

$$\omega RC = \frac{1}{\frac{R}{\omega L} + \frac{\omega L}{R}}$$

where R is the effective resistance of the tube. Calculate the value of C needed in England. Note: some algebraic tricks will give you a fast solution, however the tedious, but direct, approach of finding C to maximize  $|\mathbf{Z}_{\text{total}}|$  (and hence minimize the current) will also produce the correct answer.

26. Find the complex impedance of the RLC circuit shown to the right when it is driven by an angular frequency  $\omega = 10^5 \text{ s}^{-1}$ . What voltage would an ac voltmeter placed between the terminals measure? What current would an ac ammeter measure if connected between the two terminals (careful)?

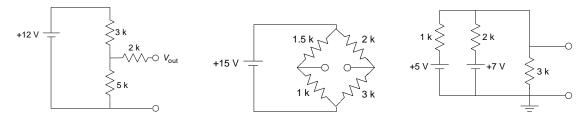

27. Find the Thévenin equivalent circuits for the below circuits. (The circles show the terminal locations.)

28. Find the Thévenin equivalent circuit for the below left circuit—the parts inside the dashed box. A 1 V battery is attached to the two terminals. Will this battery charge or discharge? How much current will flow? Sketch the equivalent circuit you determined above now with the 1 V battery attached to the two terminals.

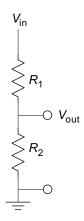

- 29. Find the Thévenin equivalent circuit for the above right voltage divider and use your equivalent circuit to answer the following questions:

- (a) What is  $V_{\text{out}}$  with nothing connected between the terminals?

- (b) What is  $V_{\text{out}}$  with a 6 k $\Omega$  resistor connected between the terminals?

- (c) When an unknown resistor is connected between the terminals,  $V_{\text{out}}$  is found to be 50% of what was found in part (a). What is the value of the unknown resistance?

- (d) When an unknown resistor is connected between the terminals,  $V_{\text{out}}$  is found to be 80% of what was found in part (a). What is the value of the unknown resistance?

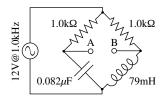

- 30. The circuit to the right is driven by a 12 V rms sinusoidal waveform at a frequency of 1000 Hz.

- (a) Calculate the (complex) voltage at A; Calculate the (complex) voltage at B.

- (b) For the two terminals A & B the equivalent ac Thévenin voltage should just be the difference between the voltage at A and voltage at B. Find this value.

- (c) Calculate the (complex) Thévenin impedance,  $\mathbf{Z}_{TH}$

- (d) Find a resistor/capacitor combination that, at this frequency, has the same impedance as you found above in c.

- (e) If terminals A & B are connected by a 1 k $\Omega$  resistor what (comlex) current would flow through it? and express it in complex rectangular form. Hint: find the effective impedances of the left and right sides of the bridge and substitute known values in right away.

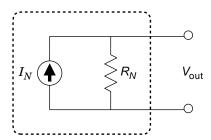

31. Norton's theorem is the sidekick of Thévenin theorem; it states that any two terminals in a complex circuit with batteries, resistors, current sources, etc., acts exactly like a resistor and current source connected in parallel between the two terminals. (As in the diagram below.) What is the Thévenin equivalent circuit for a Norton circuit? (I.e., find the Thévenin V and R for the below circuit. Be sure to explain your solution!)

- 32. Suppose you want to build a battery eliminator for a small portable radio. The radio normally draws 30 mA from four AA (penlight) cells (which are connected in series). You are willing to accept a peak-to-peak ripple of 0.2 V, and plan to use a simple bridge rectifier circuit with a transformer powered by the wall receptacle (and no voltage regulator). Draw your circuit!

- (a) What voltage transformer (rms) should you purchase?

- (b) What size filter capacitor should you purchase?

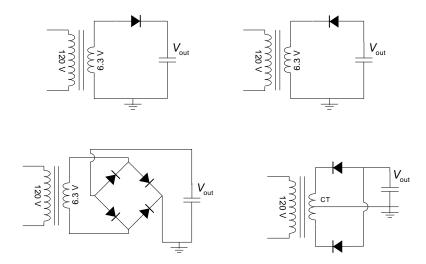

- 33. For each of the four power supply circuits shown below, find the output d.c. voltage. (All the transformers produce an rms output voltage of 6.3 V; note that the last transformer is center tapped.) For both circuits on the left: if  $C = 4700 \,\mu\text{F}$  and a d.c. current of  $I = 0.5 \,\text{A}$  is being drawn from the power supply, report the d.c. droop and a.c. ripple.

- 34. You want to make battery-based power supply for a digital (+5 V) circuit that draws 0.5 A. A 7805 voltage regulator will be used to reduce the battery's voltage to the required +5 V. Common high-capacity, lead-acid batteries come in 12 V and 6 V versions. Which must you use? How much power (heat) will be dissipated in the 7805?

- 35. In lab you have made +5 V power supplies by voltage dividing a +15 V supply and by using a 7805. How is the 7805 power supply superior to the voltage divider power supply?

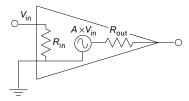

# 36. Generic Amplifier I — Thévenin applied

The following two problems deal with a generic amplifier (see right) with voltage gain A, input impedance  $R_{\rm in}$ , and output impedance  $R_{\rm out}$  driven with a sine wave input.

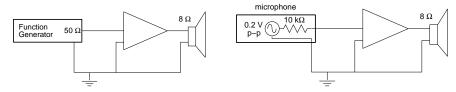

(a) A function generator with an output impedance of 50  $\Omega$ , and a 8  $\Omega$  speaker are to be connected to the input and output of the amplifier (see below left). The amplifier has a gain of 30 dB with an input impedance of 150  $\Omega$  and an output impedance of 16  $\Omega$ ). The function generator is connected to a scope and its output is adjusted to 0.2 V peak-to-peak. Assuming the speaker acts exactly like an 8  $\Omega$  resistor, find the power dissipated in the speaker.

- (b) A microphone with a Thévenin equivalent circuit of a 0.2 V peak-to-peak voltage source in series with  $10 \text{ k}\Omega$ , drives the above circuit instead of the function generator. Find the power dissipated in the speaker.

- (c) The same microphone drives a unit-gain (A=1) amplifier with an input impedance of 1 M $\Omega$  and an output impedance of 1  $\Omega$ . Find the power dissipated in the speaker.

- (d) If the microphone is directly connected to the speaker, what power will be dissipated in the speaker? Why does direct connection produce less output power than the follower?

# 37. Generic Amplifier II — Thévenin applied

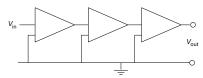

(a) Consider a circuit that consists of three identical generic amplifiers (gain: A, input impedance:  $R_{\rm in}$ , output impedance:  $R_{\rm out}$ ) cascaded together. What is the formula for the open-circuit voltage gain of the circuit?

(b) Assume that two identical amplifiers (gain 10, input impedance 1 k $\Omega$ , output impedance 100  $\Omega$ ) are capacitively coupled with a 0.1  $\mu$ F capacitor (see below, left). What is the high frequency open-circuit gain of the system? At low frequency the gain will be less. At what frequency will the gain be 3 dB less than at high frequency?

- (c) Two identical amplifiers are directly-coupled as shown above right. The amps have an input capacitance of 200 pF, output resistance of 100  $\Omega$ , and gain of 10. What is the low frequency open-circuit gain of the system? At high frequency the gain will be less. At what frequency will the gain be 3 dB less than at low frequency?

- 38. Given a function generator, resistance substitution box (variable resistor), generic amp, and scope connected to the generic amp's output, describe how you could measure  $R_{\rm in}$  in lab. Draw a schematic diagram showing the circuit used to measure  $R_{\rm in}$ . Describe the process and draw a schematic diagram showing the circuit used to measure  $R_{\rm out}$ .

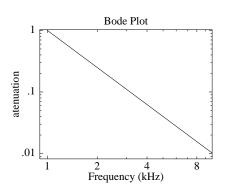

39. Bode Plot slope: dB/octave

The given Bode Plot (a log-log plot of attenuation as a function of frequency) looks like a straight line (and hence is a power law: attenuation= $Af^B$ ). What is the slope of this line in dB/octave? What is the corresponding power B?

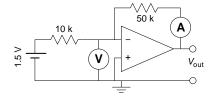

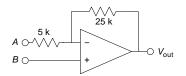

40. In the below left diagram, assume the op-amp is ideal. Report:  $V_{\text{out}}$  and the the voltmeter and ammeter readings.

- 41. In the above right diagram...

- (a) If B is grounded and A is used as the amplifier input, what is the voltage gain (including sign) and the input impedance?

- (b) If A is grounded and B is used as the amplifier input, what is the voltage gain (including sign) and the input impedance?

- 42. Design an inverting amplifier circuit with an input impedance of 5 k $\Omega$  and a gain of -20.

- 43. Design a multiple op-amp circuit that performs the following bit of arithmetic with voltage sources A, B, and C.

$$V_{\text{out}} = A + 2B - 3C$$

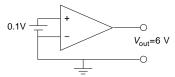

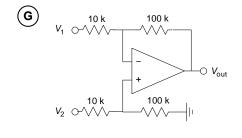

44. The circuits shown right show the results of applying various inputs to a differential amplifier.

- (b) What is the common-mode gain?

- (c) What is the Common Mode Rejection Ratio (CMRR)?

- (d) Express the CMRR in terms of dB.

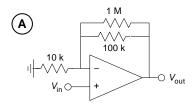

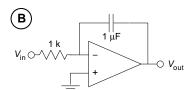

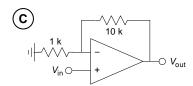

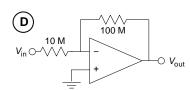

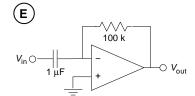

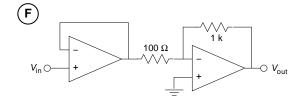

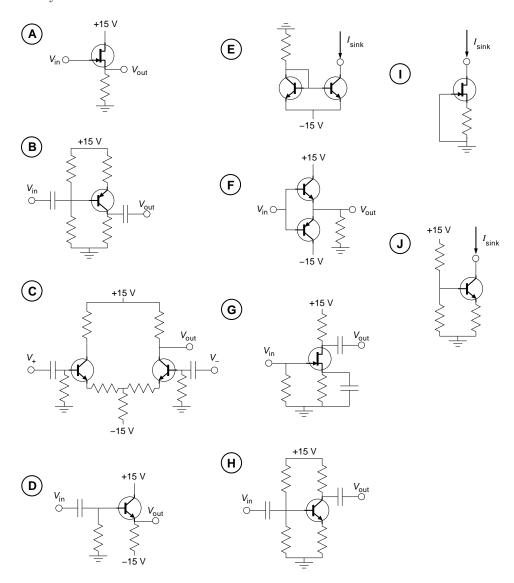

- 45. For each of the below circuits built with ordinary op-amps, indicate with a lower-case letter any and all of the following properties that apply to it.

- (a) High input impedance (>  $5M\Omega$ )

- (b) Low input impedance ( $< 5k\Omega$ )

- (c) Inverting amplifier

- (d) Non-inverting amplifier

- (e) Absolute value of gain is 10 ( $\pm 1\%$ )

- (f) Follower

- (g) Differentiator

- (h) Integrator

- (i) This circuit won't work (explain briefly why)

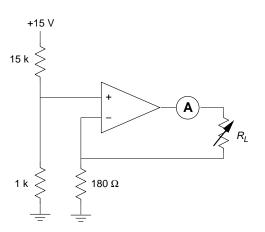

#### 46. Constant current source

In lab you built the circuit to the right using a 411 and  $\pm 15$  V power supplies. The specs of a 411 can be found HH p. 202–3. Calculate the expected ammeter reading. Calculate the largest  $R_L$  for which the current is constant. If the 180  $\Omega$  resistor were replaced with a 18  $\Omega$ , what problem would occur? If the 1 k resistor were replaced with a 4.7 k, would a problem occur?

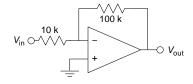

### 47. 411 Op-amp

In the circuit displayed to the right, the op-amp is a 411. What is  $f_{-3\mathrm{dB}}$  for this circuit? (Hint: HH Figure 4.31 p. 193). What is the output impedance at  $f_{-3\mathrm{dB}}$ . (Hint: 411 data sheet in Appendix K in H&H.) What is the input impedance?

48. One way of making a sinusoidal output, is to start with an easily produced wave shape (square or triangle) and filter out—as much as possible—the harmonics. The Fourier series (which shows the harmonic content) of symmetrical, unit-amplitude square and triangle waves are:

square =

$$\frac{4}{\pi} \sum_{n=1,3,5...} \frac{1}{n} \sin(n\omega t)$$

triangle =  $\frac{8}{\pi^2} \sum_{n=1,3,5} \frac{(-1)^{(n-1)/2}}{n^2} \sin(n\omega t)$

Assume that  $f_{-3dB}$  is set to the fundamental (n=1) frequency and the aim is to reduce the next (non-zero) harmonic amplitude (here, n=3) to 1% of the fundamental's amplitude. Specify the dB/octave required to do this job for (a) the square wave and (b) the triangle wave. (Hint: start by finding how many octaves 3f is above f.)

49. A full-wave rectified signal (of the usual f=60 Hz line voltage, where below  $\omega=2\pi f$ ) has the Fourier series:

full-wave =

$$\frac{2}{\pi} - \frac{4}{\pi} \sum_{n=2,4,6,...} \frac{1}{n^2 - 1} \cos(n\omega t)$$

The aim is to reduce the n=2 (i.e., 120 Hz) amplitude to 1% of the dc voltage level using a simple RC filter (at 6 dB/octave). Find the filter's  $f_{-3\text{dB}}$ . Note: in the usual circuit (with diodes and a capacitor, and with no current draw), the capacitor holds the peak value of the rectified wave (here 1) rather than the average value (here  $2/\pi$ ).

- 50. Design a 555 oscillator producing a tone of frequency 440 Hz. Make a schematic diagram of your design (and be sure to report how every pin on the 555 is connected).

- 51. A 555 is connected as an oscillator (e.g., HH Fig. 5.33, p. 287) using a 0.1  $\mu$ F capacitor and two 1 k $\Omega$  resistors, and powered with +10 V.

- ions?

- (b) Make a moderately accurate sketch of of the output signal (pin 3) as a function of time.

- 52. The *duty cycle* of an asymmetrical square wave is usually defined as the ratio of the time the signal is high to the overall period of the wave.

- (a) Find a formula, expressed in terms of the resistor values, for the duty cycle of a 555 (as an oscillator) .

- (b) Your formula should suggest that making one resistor  $0~\Omega$  would make a symmetrical square wave (duty cycle of 50%). Why is this a bad idea?

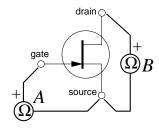

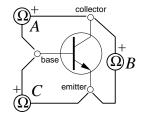

### 53. n-channel JFET and Ohmmeter

- (a) Two resistance measurements (A and B) are made sequentially with one ohmmeter following the connections as shown in the diagram to the right. The + (red) terminal is connected exactly as shown. Each reading is expected to be either a "small" resistance (say, < 5 k $\Omega$ ) or a "large" resistance (say, > 5 M $\Omega$ ). For each connection, report which will be observed and why.

- (b) Suppose now (in both cases) the + and (red and black) ohmmeter leads are swapped. For both situations, report whether the new readings are "small" or "large" and why.

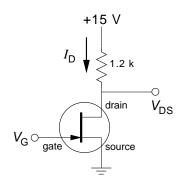

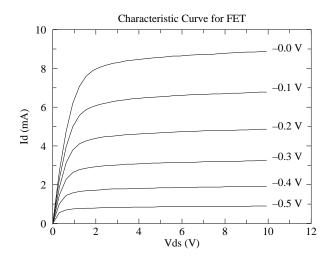

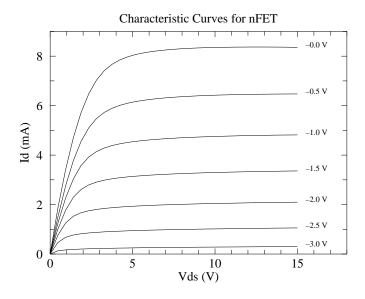

### 54. nJFET Characteristic Curves<sup>1</sup>

The file fet4.pdf on the class web site contains the characteristic curves of an n-channel junction field-effect transistor (nJFET). Each characteristic curve is labeled with the corresponding gate voltage  $(V_G)$ . Using the plot estimate the zero-gate-voltage drain current  $(I_{DSS})$  and gate source cutoff voltage  $(V_{TO})$  or  $V_{GS,off}$ , a.k.a. pinchoff voltage  $V_P$ ). This FET is to be used in the circuit to the right. Directly on hardcopy of fet4.pdf: draw the load line for this circuit and label "Q" your selected quiescent point. What d.c. gate voltage is required for your Q point (i.e., gate bias voltage)? If the gate voltage is 0.5 V above your gate bias voltage, what drain current  $(I_D)$  and drain-source voltage  $(V_{DS})$  would result? If the gate voltage is 0.5 V below your gate bias voltage, what  $I_D$  and  $V_{DS}$  would result? Use this result to calculate the gain of the circuit (i.e., a 1 V peak-to-peak input at the gate results in what peak-to-peak output signal at the drain).

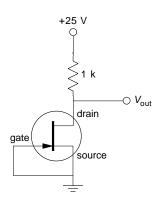

# 55. n-channel JFET $I_{DSS}$

The n-channel junction field-effect transistor (nJFET) used in the circuit to the right has the characteristic curves recorded in the file fet4.pdf on the class web site. Each characteristic curve is labeled with the corresponding gate voltage  $(V_G)$ . Report the voltage  $V_{\text{out}}$  (relative to ground).

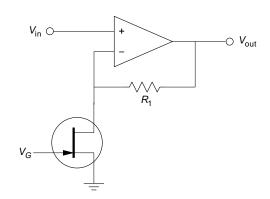

# 56. Variable (voltage-controlled) Gain Amplifier

The file fet4b.pdf on the class web site contains the *small*  $V_{DS}$  characteristic curves of an n-channel junction field-effect transistor (nJFET). Each characteristic curve is labeled with the corresponding gate voltage  $(V_G)$ . This FET is used in the circuit to the right.

- (a) If  $R_1 = 10 \text{ k}\Omega$  and  $V_G = 0 \text{ V}$ , what is the gain of this circuit?

- (b) If  $R_1 = 10 \text{ k}\Omega$  and  $V_G = -1.5 \text{ V}$ , what is the gain of this circuit?

- (c) If  $R_1 = 100 \text{ k}\Omega$  and  $V_G = 0 \text{ V}$ , what is the gain of this circuit?

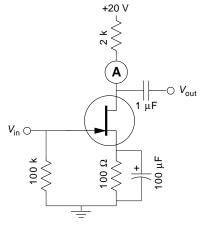

# 57. Consider the common source FET amplifier shown right:

- (a) Somebody claims the ammeter reads 20 mA. Explain why this is impossible and report what the ammeter should read if the circuit is properly designed. (Assume this current in answering the remaining questions.)

- (b) What is the gate bias voltage?

- (c) If the transconductance is 0.01  $\mho$ , what is the gain?

- (d) What is the input impedance?

- (e) What is the output impedance?

¹http://www.physics.csbsju.edu/trace/nFET.CC.html describes in detail these characteristic curves and the parameters used to describe them.

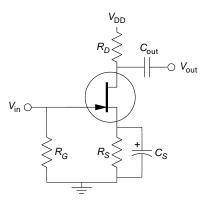

58. A common source amplifier (see below right) is to be built using an n-channel JFET with the characteristic curves shown below left. For each component of this amp, report a value and how that value was determined (often just a formula). Report your gate bias voltage, transconductance at that voltage, amplifier gain and input and output impedances.

59. Three resistance measurements (A, B, and C) are made sequentially with one ohmmeter as shown in the diagram to the right. The + (red) terminal is connected exactly as shown. For each connection, report whether the ohmmeter reports a "small" resistance (say,  $< 5 \text{ k}\Omega$ ) or a "large" resistance (say,  $> 5 \text{ M}\Omega$ ). Report the basis for your expectations.

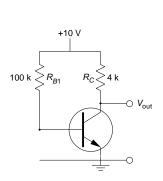

60. In the circuit shown below left,  $V_{\text{out}}$  is 5 V. What is  $h_{FE}$  (a.k.a.  $\beta$ )? How much power is dissipated in the transistor?

- 61. In the circuit shown above right,  $h_{FE}$  is 80. Report the reading expected on the voltmeters  $V_1$  and  $V_2$  and the ammeter A. If  $h_{FE}$  is 160, what will the meters report?

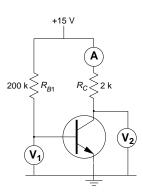

- 62. Assuming that the transistor shown has  $h_{FE} = 50$ , find  $V_{\text{out}}$  for the below circuits. If the transistor turns out to have  $h_{FE} = 100$ , find the new values of  $V_{\text{out}}$ .

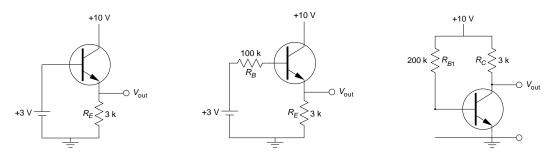

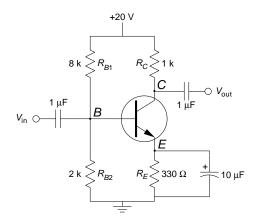

- 63. In the circuit shown right, the transistor has  $h_{FE} = 150$ . The amplifier should have a low frequency response that extends down to 60 Hz. Calculate:

- (a) the base current

- (b) the collector current

- (c)  $r_e$

- (d) the collector-emitter voltage

- (e) the voltage gain

- (f)  $C_{\rm in}$

- (g)  $C_{\text{out}}$

- 64. In the circuit shown right, begin by assuming that the transistor's  $h_{FE} = \beta$  is so large that the base current can be neglected.

- (a) Calculate the voltages at B, E, and C.

- (b) If the base current is *not* negligible, how will the voltages at B, E, and C be affected? That is for the points B, E, and C, report if the voltage will increase, decrease, or stay the same.

- (c) If  $V_C$  is changed by 1 V, find  $V_E$  and  $V_B$ .

- (d) Report the Thévenin equivalent circuit for the 8k+2k voltage divider. If the voltage divider is in fact producing the output voltage given by  $V_B$  in part (c), how much current must the divider be sourcing?

- (e) If the base current is given by that found in part (d) and the collector current given by the situation in (c), what is the  $\beta$  of the transistor?

- (f) Repeat the calculation of the previous part, but this time assume that the voltage divider is 80k+20k.

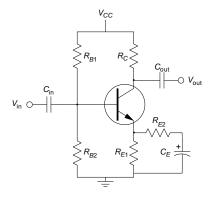

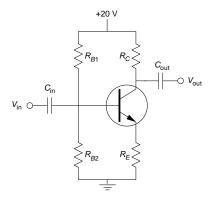

65. Design a BJT amplifier using the circuit shown right. You should provide all component values and the calculations that support those values. (This will require a choice for  $f_{-3\text{dB}}$ .) Calculate the input and output impedance. The circuit constraints are: voltage gain of 20, output impedance < 5 k $\Omega$ , input impedance > 15 k $\Omega$ , and that your base bias circuit will work for a transistor with  $\beta = 100$  or  $\beta = \infty$ .

66. Design a BJT amplifier for a gain of 10 and an output impedance of 5 k $\Omega$  (i.e., find all the values for the components shown). Design the base bias assuming  $\beta=150$ . Assume the amplifier is to be used for audio frequencies in the range 20–20,000 Hz. Calculate the input impedance.

How robust is your design, that is, how small could your actual transistor  $\beta$  be and still have the circuit work? Assume that the actual transistor used results in a  $V_E$  just 70% of your design  $V_E$  (this would often cause problems), and then calculate the actual transistor's  $\beta$ .

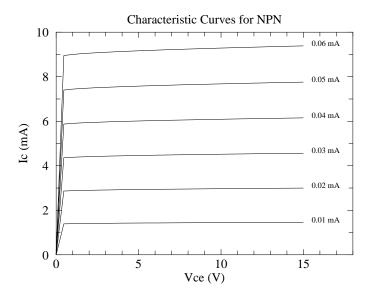

- 67. (a) The following page has characteristic curves for BJT and FET. Directly on the NPN characteristic curves, label the region where the transistor is saturated, on, and off. Draw the schematic diagram symbol for a PNP bipolar transistor and label each lead with its proper name.

- (b) Directly on the n-channel characteristic curves, label the ohmic region, the region where the FET is cut-off (a.k.a. sub-threshold), and where the FET is active. (Note: what I call an "active" FET, is often called "saturated" or "pinched-off". Of course, "saturated" for a FET is different from "saturated" for a bipolar.) Draw the schematic diagram symbol for a p-channel FET and label each lead with its proper name.

68. Consider the below characteristic curves of an npn bipolar transistor. Calculate  $h_{fe} = \beta$ . Assume the npn transistor is part of a common emitter amplifier with a supply voltage of 12 V. Directly on the below plot, draw in the load line for a 2 k $\Omega$  collector resistor, and mark a nice operating point Q. At Q, what is the change in the collector voltage  $\Delta V_{CE}$  for a change in the base current  $\Delta I_B = .01$  mA? Calculate  $h_{ie}$  using your operating point's base current. What change in the base voltage  $\Delta V_{BE}$  will accompany the change in the base current  $\Delta I_B = .01$  mA? Calculate the ac voltage gain:  $\Delta V_{CE}/\Delta V_{BE}$ . At your operating point, how much power is dissipated in the transistor?

69. Consider the below characteristic curves of an n-channel JFET. What is  $I_{DSS}$ ? Calculate g for  $V_{GS} = -1.5$  V. Estimate the threshold gate voltage. Assuming a supply voltage of 12 V, draw directly on the below plot the load line for a 2 k $\Omega$  drain resistor characteristic curves. Label Q the operating point obtained with  $V_{GS} = -1.5$  V. What is the quiescent drain current? How much power is dissipated in the transistor in this quiescent state? Design a common source amplifier (see problem 57) using this FET. Your schematic diagram of the circuit should show all component values and input and output locations. As usual, you will bias the gate (here to  $V_{GS} = -1.5$  V) using a source resistor (bypassed with a capacitor  $C_S$  so the ac signal doesn't see it). What value of  $C_S$  should you use if the amplifier is to amplify signals with frequencies between 100 and 10,000 Hz? Report the expected voltage gain and both input and output impedance.

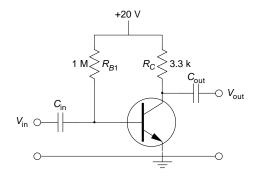

70. Describe briefly what each of the below circuits does.

71. Biasing—Voltage Divider Design: Using a supply voltage ( $V_{CC} = V_{\rm in} = 20$  V) you aim to provide a base current of  $I_B = 20~\mu{\rm A}$  at a base voltage of  $V_B = V_{\rm out} = 2$  V (and hence emitter voltage  $V_E = 1.4$  V) for a BJT amplifier as in problem 66. The impedance looking in the base is expected to be  $\beta \times R_E = 100 \times 700~\Omega$ , and the current,  $I_E$ , through  $R_E$  is expected to be  $V_E/R_E = 2$  mA. For a well designed circuit we expect  $V_{CE} = \frac{1}{2}V_{CC}$ , however if the actual  $I_E$  does not match the designed  $I_E$ ,  $V_{CE}$  will be changed with:

$$\Delta V_{CE} = -(R_E + R_C)\Delta I_E$$

or, dividing by the designed  $V_{CE \text{ design}} = \frac{1}{2} V_{CC}$ , we have:

$$\frac{\Delta V_{CE}}{V_{CE \text{ design}}} \approx \frac{\Delta I_E}{I_{E \text{ design}}} = \frac{\Delta V_E}{V_{E \text{ design}}}$$

where we've used  $I_{E \text{ design}} = \frac{1}{2}V_{CC}/(R_E + R_C)$ .

### Problem 71 continued:

- A. Method A: As suggested by H&H, design the voltage divider with a Thévenin equivalent resistance of  $\frac{1}{10} \times$  the impedance looking in the base and a Thévenin equivalent voltage of the desired  $V_B$ . With this bias design, the design  $V_B = V_{\rm out}$  is only achieved with zero  $I_B$ , i.e.,  $\beta \to \infty$ , but, because of the impedance mismatch,  $V_{\rm out}$  should be 'close' to the designed value even if  $I_{B \text{ design}}$  is sourced.

- i. Find the required  $R_1$  and  $R_2$ .

- ii. If 20  $\mu$ A is drawn from  $V_{\text{out}}$ , what is the resulting  $V_{\text{out}}$ ?

- iii. What is the resulting  $\Delta V_E$  and  $\Delta V_E/V_{E \text{ design}}$ ?

- iv. If 40  $\mu$ A is drawn from  $V_{\text{out}}$ , what is the resulting  $\Delta V_E/V_{E \text{ design}}$ ?

- B. Method B: Design the voltage divider so that  $V_{\text{out}} = 2 \text{ V}$ , with  $10 \times I_B$  through  $R_1$  and  $9 \times I_B$  through  $R_2$  (and an assumed  $1 \times I_B$  exiting through  $V_{\text{out}}$ ).

- i. Find the required  $R_1$  and  $R_2$ .

- ii. If  $\beta \to \infty$ , in fact no current would exit at  $V_{\rm out}$  and as a result  $V_{\rm out}$  would rise above 2 V. Find  $V_{\rm out}$  in this circumstance. What is the resulting  $\Delta V_E/V_{E \ {\rm design}}$ ?

- iii. If 40  $\mu$ A is drawn from  $V_{\text{out}}$ , what is the resulting  $\Delta V_E/V_{E \text{ design}}$ ?

# 72. Define the following electronic terms:

- A. no-load

- B. current source

- C. open circuit

- D. short circuit

- E. pot

- F. choke

- G. condenser

- H. Norton/Thévenin

- I. output impedance

- J. lead/lag

- K. Bode plot

- L. Wheatstone bridge

- M. xy scope mode

- N. full-wave/half-wave rectification

- O. bridge rectification

- P. center-tapped transformer

- Q. linear power supply

- R. switching power supply

- S. load regulation

- T. voltage droop (power supply)

- U. stiff (voltage source)

- V. diode cathode/anode

- W. PN junction

- X. p-type/n-type material

- Y. minority carrier

- Z. negative feedback

- a. common mode rejection ratio

- b. slew rate

- c. open loop gain

- d. differential amplifier

- e. compensated op-amp

- f. virtual ground

- g. amplifier  $f_{-3dB}$

- h. biasing

- i. blocking/bypass capacitor

- j. active load

- k. FET, MOSFET

- l. n-channel, p-channel

- m. enhancement/depletion

- n. drain/gate/source

- o. "common" in e.g., common source amp

- p. admittance

- q.  $y_{fs}, y_{os}$

- r. g, transconductance

- s. Bipolar transistor (NPN, PNP)

- t. collector/base/emitter

- u. hybrid parameter

- v.  $h_{fe}$ ,  $h_{oe}$ ,  $h_{ie}$ ,  $r_e$

- w.  $\beta$ , current gain

- x. current mirror

- y. push-pull

- z. Darlington