P: 25, 76,30,38,48 HIT 60.23,10.24 old exa # \$15,6 E, Ez E3 C, Cz C3 4 D 25 % 0 1 X X 0 0 1 6 0 0 \ X 1 0 0 0 0 1 0 0 1 0 0 1 0 0 1 1 0 0 0 1 100 0 1 0 6 1 0 Choice: l O X down! 0 1 0 0 1 0 0 0 1 X X X O OO 4 = E, C, (C2+C3) + E2 C2 C, C3 26) a) Not sync as #3 clocked by Q2 0 1 6 -7 11 11 10 B C D 100 11 11 00 0 0 0 3 11 11 00 JK JK SR

b) A toggles

DCBA

0000 - 0001 - 0010 - 0011 - 0100 - 0101

0) DCBA 3 0010 3 0100 3 0110.

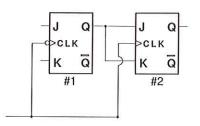

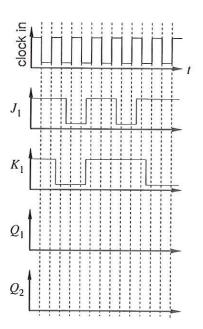

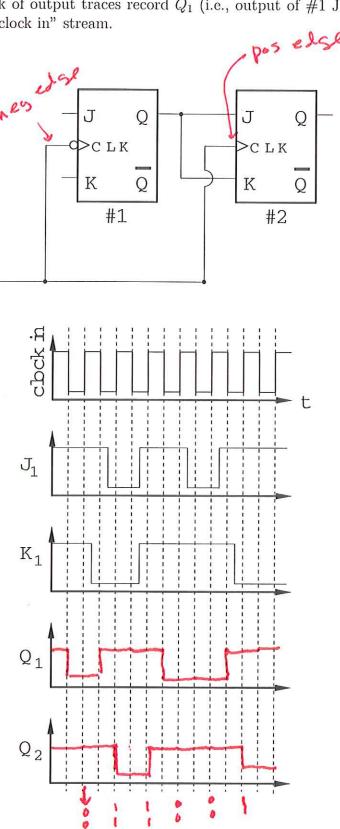

29. Consider the below circuit using pair of JKFF. Directly on this sheet appropriately (i.e., correctly given the circuit diagram) label each JKFF "negative edge triggered" or "positive edge triggered". At the start of this clock sequence Q<sub>1</sub> and Q<sub>2</sub> are both HIGH; controls J<sub>1</sub> and K<sub>1</sub> are changed as shown in the below plot stack and controls J<sub>2</sub> and K<sub>2</sub> are determined by the circuit. Directly on the below stack of output traces record Q<sub>1</sub> (i.e., output of #1 JKFF) and Q<sub>2</sub> for the given "clock in" stream.

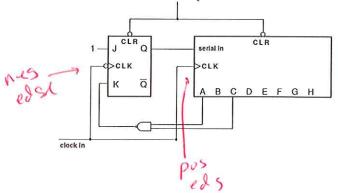

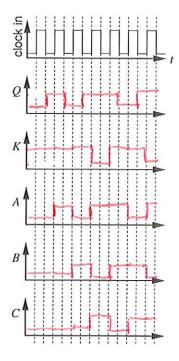

30. Consider the below circuit using a shift register and a JKFF. The chips are cleared and the clock started. Graph (on this page) a stack of output traces: Q, K, A, B, and C underneath the clock input stream. Include at least 7 clock cycles.

- 31. For this problem you will need the pinout and function table of the '121 monostable. The required information can be found in Fig. 7.59 HH p. 462 and/or sn74121.pdf (downloaded from ti.com and placed in the class web site). Design circuits (and record exact wiring diagrams—including pin numbers) that do the following:

- (a) make a 20  $\mu$ s pulse on a positive edge

- (b) make a 20  $\mu s$  pulse delayed by 1 ms from a negative edge

- (c) make a 50 kHz symmetrical square wave

38. We return here to the problem of finding circuits for state diagrams. Recall that the current state must totally control the following state. But what if we want various futures for a state in various circumstances?

The Morse Code is a bit unusual encoding of letters in that the letters require differing numbers of dot/dashes from one (E=dot=0, T=dash=1) to four (e.g., Q=dash-dash-dot-dash). If we restrict ourselves to the eight letters expressed with 3 bit Morse Code expressions: (D=100, G=110, K=101, O=111, R=010, S=000, U=001, W=011), we can make some odd sentences like: DORKS GROK SORROW. Imagine a circuit that cycles through these letters (i.e., D $\rightarrow$ O $\rightarrow$ R $\rightarrow$ K $\rightarrow$ S $\rightarrow$  etc.). However see that the four Os have different targets: O $\rightarrow$ R, O $\rightarrow$ W. Therefore the *circuit* must distinguish four different types of O (but of course the display will show the same lettershape for each O state). Thus:

$$D \rightarrow O_0 \rightarrow R_0 \rightarrow K_0 \rightarrow S_0 \rightarrow G \rightarrow R_1 \rightarrow O_1 \rightarrow K_1 \rightarrow S_1 \rightarrow O_2 \rightarrow R_2 \rightarrow R_3 \rightarrow O_3 \rightarrow W$$

Each state will now be labeled with five bits  $Q_1Q_2Q_3Q_4Q_5 - Q_3Q_4Q_5$  specifying the lettershape and  $Q_1Q_2$  distinguishing the various 'identical' letters. Fill in the below table so it displays the desired cycle and the  $D_i$  required to generate it. Find a boolean expression for one of the  $D_i$  in terms of the  $Q_i$ .

|     | $Q_1$ | $Q_2$ | $Q_3$ | $Q_4$ | $Q_5$ | $  D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ |

|-----|-------|-------|-------|-------|-------|---------|-------|-------|-------|-------|

| D . | 0     | 0     | 1     | 0     | 0     | 0       | U     | ı     | ı     | 1     |

| 0   | 0     | 0     |       |       | 1     | 0       | U     | O     | 1     | 0     |

| R   | O     | O     | Ó     | - 1   | 0     | 0       | U     | l     | O     | -     |

| K   | 0     | 0     |       | 0     | _ \   | U       | 0     | 0     | 0     | 0     |

| 5.  | O     | 0     | U     | 0     | 0     | 0       | 0     | L     | - (   | 0     |

| G.  | O     | 0     | 1     | l     | 0     | 6       | (     | O     | t     | 0     |

| R   | U     | l     | 0     | 1     | 0     | 0       | ı     | (     | l     | 1     |

| 0   | U     | (     | 1     | - 1   | 1     | 6       | 1_    | 1     | 0     | -     |

| K   | u     | i_    | 1     | 0     | 1     | G       | 1     | 0     | 0     | 0     |

| 5   | a     | - 1   | 0     | 0     | O     | Le      | 0     | - 1   | · L   | 1     |

| U   | ı     | b     | ı     | l     | ı     |         | 0     | O     |       | 0     |

| 2   | ı     | 0     | O     | ι     | O     | /       | 1     | - 0   | (     | 0     |

| R   | ·     | l     | U     | ι     | 0     | \ i     | 1     | ·     | 1 1   |       |

| 0   | ·     | 1_    |       | ı     | 1     | 16      | ) (   | , (   | , l   |       |

| W   | 0     | D     | U     | l     | (     | 10      | 0     |       |       |       |

39. HH describes more than half a dozen temperature transducers. Pick out three of these and 'compare and contrast' them—that is report their advantages and disadvantages. Describe a situation in a physics lab requiring a temperature measurement and report which transducer you would select and why

address to the Mux fie the same-humber D line

as regulated in TT

Be have fin fre

pial6 = Vcc

pin6 = 6 NO

100 D1 3 1

pin7 = stroke = 6 ND

A Be | Maney Pin ) DZ 1 1 0 P5 0 11

Note: ABC in problem differed

order from ABC in spec sheet

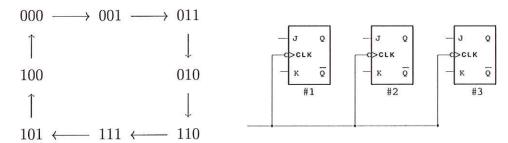

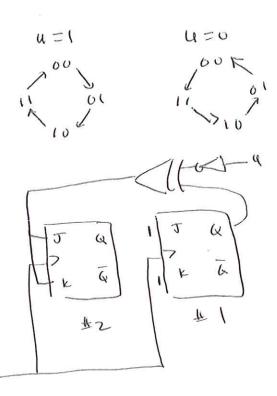

4. The Gray code state diagram of the three binary digits:  $Q_1Q_2Q_3$  is displayed below:

Your job is to design a synchronous circuit built from three edge-triggered JKFFs that follows the above state diagram, where the three binary digits  $Q_1Q_2Q_3$  are the outputs of distinct edge-triggered JKFFs. You will need to determine the gate arrangement needed to make this cycle run, i.e., connecting the outputs of the three JKFFs:  $Q_i$  to the inputs of the three JKFFs:  $J_iK_i$  possibly using the usual (AND, OR,...) gates.

(a) Begin by considering the possible transitions of a single JKFF. What values of JK allow a particular transition? Fill in the below table. Hint: in every row either J or K will be an X for "don't care".

| Transition:           | J | K |

|-----------------------|---|---|

| $0 \longrightarrow 0$ | 0 | X |

| $0 \longrightarrow 1$ | t | γ |

| $1 \longrightarrow 0$ | X |   |

| $1 \longrightarrow 1$ | × | 0 |

(b) Now fill in the below table which displays the desired cycle.

| $Q_1$ | $Q_2$ | $Q_3$ | $J_1$ | $K_1$ | $J_2$ | $K_2$ | $J_3$ | $K_3$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | X     | 0     | Y     | 1     | γ     |

| 0     | 0     | 1     | D     | V     | ı     | X     | K     | U     |

| 0     | 1     | 1     | 0     | V     | X     | O     | X     | 1     |

| 0     | 1     | 0     | 1     | V     | У     | U     | 0     | ¥     |

| 1     | 1     | 0     | Y     | 0     | Х     | O     | ı     | ٧     |

| 1     | 1     | 1     | ×     | 0     | ٧     | l     | ¥     | U     |

| 1     | 0     | 1     | Y     | v     | U     | X     | ¥     | l     |

| 1     | 0     | 0     | X     | 1     | U     | K     | U     | K     |

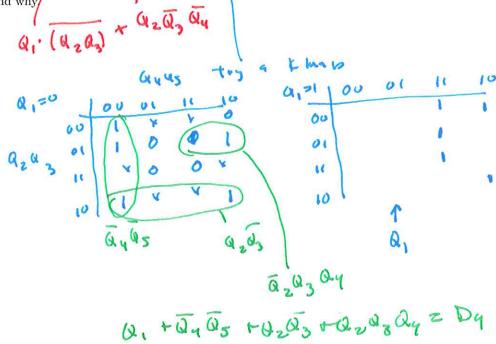

(c) Gates for  $J_1$ ,  $K_1$ ,  $J_2$ , and  $K_2$  can be fairly easily generated using two input gates and the outputs of the JKFFs. Pick one of the above  $(J_1, K_1, J_2, \text{ or } K_2)$  and find a simple expression for it in terms of the  $Q_i$  and  $\overline{Q_i}$ . Implement (construct) your expression using simple gates.

$$J_1 = Q_2 \overline{Q}_3$$

$V_2 = Q_1 \overline{Q}_3$

$V_2 = Q_1 \overline{Q}_3$

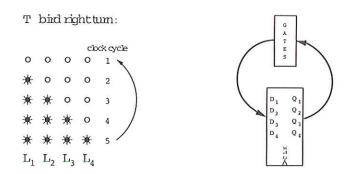

5. The rear turn indicators on old Ford Thunderbirds had a distinctive pattern in which the four segments of the indicator were illuminated sequentially, "pointing" the direction of the turn. For example, on a right-turning T-bird you would see the four segments which made up the right-rear indicator cycle as shown below:

Implement this cycle using four DFFs and external gates ( $Q_i = L_i$ ).

- (a) Draw the state diagram for this process.

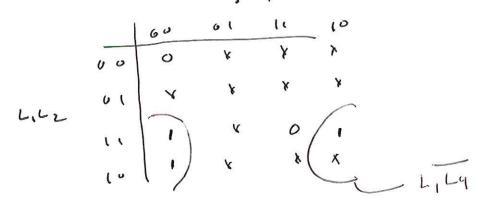

- (c) Make a Karnaugh map for  $D_2$  in terms of the four logical variables  $L_1, L_2, L_3, L_4$ . Note that there will be *lots* of Xs (don't care) entries. Circle appropriate groups to find a boolean expression for  $D_2$ . Please carefully label your Karnaugh maps so I know what each row and column of the map represents!

6. Consider the below circuit using pair of JKFF. Directly on this sheet appropriately (i.e., correctly given the circuit diagram) label each JKFF "negative edge triggered" or "positive edge triggered". At the start of this clock sequence  $Q_1$  amd  $Q_2$  are both HIGH; controls  $J_1$  and  $K_1$  are changed as shown in the below plot stack and controls  $J_2$  and  $K_2$  are determined by the circuit. Directly on the below stack of output traces record  $Q_1$  (i.e., output of #1 JKFF) and  $Q_2$  for the given "clock in" stream.

HH 10.23

| Q2 Q1 | Jz  | 1/2/ | $\mathcal{T}'$ | k,  |   |

|-------|-----|------|----------------|-----|---|

| 0 0   | 0   | X    | i              | X   |   |

| 0 (   | 1 4 | (    | X              | (   |   |

| 10    | 7   | 1    | Ó              | ۲   |   |

| (     | 3,  | (    | 10             | r   | ١ |

| 600   | i   | ١    | 0              | ) ( |   |

10.24

clock

| u   | Q 2 | 0, | $J_{\iota}$ | Kz   | 71  | K.          |

|-----|-----|----|-------------|------|-----|-------------|

| 1   | 0   | 6  | 6           | ×    | ١   | ×           |

| 1   | O   | 1  | 1           | 4    | ×   | 1           |

| - 1 | l   | U  | ¥           | 0    | t   | X           |

| i   | Ţ   | 1  | *           | 1    | X   | \           |

| 0   | 0   | 0  | 1           | X    | 1   | <b>&gt;</b> |

| Ŏ   |     | 1  | \ ×         | 0    | 1 / | γ.          |

| D   | 1   | U  | 1           | χ,   |     | ζ (         |

| C   | 0   | 1  | 1 0         |      | 1-  | )           |

|     |     |    |             |      |     | HIGH        |

|     |     |    | 46          | D Q, | l   | ,,,,,,,,    |