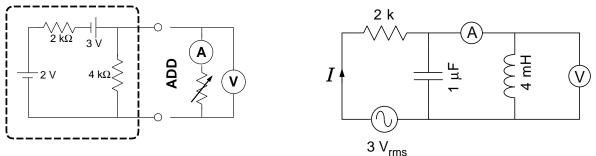

1. Find the Thévenin equivalent circuit for the two terminals connected to the circuit inside the dashed box as shown below left. The variable resistor+ammeter+voltmeter circuit shown adjacent is then connected to the two terminals. (A) If the variable resistor is set to infinite resistance, what would the voltmeter and ammeter read? (B) If the variable resistor is adjusted until the voltmeter reads exactly one half the opencircuit voltage across the terminals, what is the resistance of the variable resistor? (C) If the variable resistor is adjusted to  $10 \times$  the Thévenin resistance of the boxed circuit, what would the voltmeter and ammeter read?

- 2. The circuit shown above right is driven with an ideal 3  $V_{\rm rms}$  source at 2.5 kHz. The ammeter (A) and voltmeter (V) shown in the circuit are ideal and, like ordinary DMMs, report rms values.

- (a) Find the complex current I; report its magnitude and phase. Does the function generator's voltage lead or lag I?

- (b) Find the values reported by the two meters. (Hint: think voltage divider.)

- 3. Provide a brief definition of the following electronics terms:

- (a) voltage droop (power supply)

- (b) half-wave rectification

- (c) filter or amplifier  $f_{-3dB}$

- (d) output impedance

- (e) pot

- (f) Coupling►AC (scope)

- (g) back-biased PN junction

- (h) darlington

- (i) push-pull follower

- (j) active load

- 4. Draw the schematic circuit diagram for an op amp amplifier with a gain of -100. Report reasonable component values. Draw the schematic of an op amp amplifier using the same components with a gain of 101. Aside from the gain difference (-100)vs. 101), what important characteristic is different between these two circuits? In lab you constructed op amp amplifiers with gains of -10 and 11. Compare the  $f_{-3dB}$  of the high gain circuit to the  $f_{-3dB}$  of the lower gain circuit.

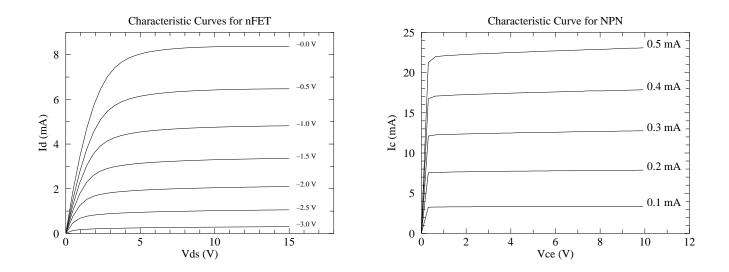

5. Consider the above left characteristic curves of an n-channel FET. Report this FET's  $I_{DSS}$ . Calculate transconductance g for  $V_{GS} = -1.5$  V. Estimate (eyeball) the threshold gate voltage. Directly on the above plot label the ohmic region, the region where the FET is cut-off (a.k.a. sub-threshold), and where the FET is active. (Note: what I call an "active" FET, is often called "saturated" or "pinched-off". Of course, "saturated" for a FET is different from "saturated" for a bipolar.) Draw the schematic diagram symbol for a n-channel jFET and label each lead with its proper name.

Consider the above right characteristic curves of an npn bipolar transistor. Calculate  $h_{FE} = \beta$ . Directly on the above npn characteristic curves, label the region where the transistor is saturated, on, and off. Draw the schematic diagram symbol for a PNP bipolar transistor and label each lead with its proper name.

- 6. Assume the above left FET is part of a common source amplifier with a supply voltage of 18 V. Provide a schematic circuit diagram of this circuit showing all the required components and input and output locations. Record/derive all component values. Draw—directly on the above characteristic curves— the load line for a 2.7 k $\Omega$  drain resistor. Label **Q** the operating point with  $V_{GS} = -1.5$  V. What is the quiescent drain current? How much power is dissipated in the transistor in this quiescent state? Bias the gate to  $V_{GS} = -1.5$  V using a source resistor  $R_S$  (bypassed with a capacitor so the ac signal doesn't see it). What value of  $R_S$  should you use for your circuit? What value bypass capacitor is required if the amplifier is to operate on audio signals: 20– 20,000 Hz. What value output capacitor is required? Report the expected voltage gain and the output impedance.

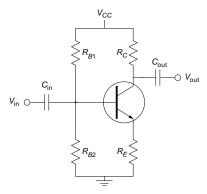

- 7. Design a BJT amplifier shown right with  $V_{CC} = 25$  V, ac voltage gain  $A_V = -15$ , and output impedance  $Z_{out} = 5.1$  k. The amplifier should work for frequencies in the range 20–20,000 Hz. Report all of the component values and additionally the input impedance  $Z_{in}$ . Assume  $\beta = 150$  when/if that value is needed. Report your circuit's quiescent emitter voltage  $V_E$ both for  $\beta = 150$  and  $\beta = \infty$ .